# **SIEMENS**

# SICOMP IMC

# **Industrial Microcomputer**

System Manual

Table of Contents

| SICOMP IMC System                      | 1  |

|----------------------------------------|----|

| SMP16 System                           | 2  |

| AMS System                             | 3  |

| PCI System                             | 4  |

| Compact Computer                       | 5  |

| Assembling Center                      | 6  |

| Power Supplies                         | 7  |

| System Layout                          | 8  |

| Software                               | 9  |

| Communication                          | 10 |

| Commissioning, Testing and Debugging   | 11 |

| Environmental Requirements             | 12 |

| Service/System Consulting/<br>Training | 13 |

|                                        |    |

Glossary/Abbreviations

6AR1950-7AA00-2CA0

#### **Safety Guidelines**

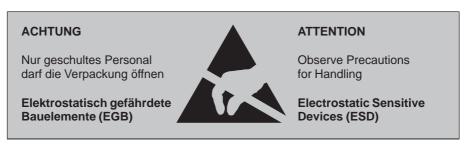

This manual contains notices which you should observe to ensure your own personal safety, as well as to protect the product and connected equipment. These notices are highlighted in the manual by a warning triangle and are marked as follows according to the level of danger:

#### Danger

indicates that death, severe personal injury or substantial property damage **will** result if proper precautions are not taken.

#### Warning

indicates that death, severe personal injury or substantial property damage **can** result if proper precautions are not taken.

#### Caution

indicates that minor personal injury or property damage can result if proper precautions are not taken.

#### Note

draws your attention to particularly important information on the product, handling the product, or to a particular part of the documentation.

#### **Qualified Personnel**

The device/system may only be set up and operated in conjunction with this manual. Only **qualified personnel** should be allowed to install and work on this equipment. Qualified persons are defined as persons who are authorized to commission, to ground, and to tag circuits, equipment, and systems in accordance with established safety practices and standards.

#### Trademarks

SICOMP® is a registered trademark of SIEMENS AG.

Some of the other designations used in this publication may also be registered trademarks; the owner's rights may be violated if they are used by third parties for their own purposes.

#### Copyright Siemens AG 1998 All rights reserved

The reproduction, transmission or use of this document or its contents is not permitted without express written authority. Offenders will be liable for damages. All rights, including rights created by patent grant or registration of a utility model or design, are reserved.

Siemens AG Automation and Drive Technology Combination technology P.O. Box 2355, D-90713 Fuerth

#### **Disclaimer of Liability**

We have checked the contents of this manual for agreement with the hardware and software described. Since deviations cannot be precluded entirely, we cannot guarantee full agreement. However, the data in this manual are reviewed regularly and any necessary corrections included in subsequent editions. Suggestions for improvement are welcomed.

© Siemens AG 1998 Subject to change without prior notice

# **Table of Contents**

| 1 | SICOMP                                                             | IMC System                                                                                                                                                                                                                                             | 1–1                                                          |

|---|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| 2 | SMP16 S                                                            | System                                                                                                                                                                                                                                                 | 2–1                                                          |

|   | 2.1                                                                | System Overview                                                                                                                                                                                                                                        | 2–2                                                          |

|   | 2.2<br>2.2.1<br>2.2.2                                              | Function Description         Bus Elements         System Architecture                                                                                                                                                                                  | 2–5<br>2–5<br>2–6                                            |

|   | 2.3                                                                | General Technical Description                                                                                                                                                                                                                          | 2–8                                                          |

|   | 2.4<br>2.4.1<br>2.4.2                                              | Signals of the Bus InterfaceExplanation of Table 2-4Description of the Bus Signals                                                                                                                                                                     | 2–9<br>2–10<br>2–11                                          |

|   | 2.5<br>2.5.1<br>2.5.2<br>2.5.3<br>2.5.4<br>2.5.5<br>2.5.6<br>2.5.7 | Data Transmission on the Bus<br>General Description<br>Data Bus Length<br>Control of the Data Bus length with IOCS16* and MEMCS16*<br>Read Operations<br>Write Operations<br>Slave-Master Synchronization with RDYIN<br>Command Delays and Wait Cycles | 2–19<br>2–19<br>2–20<br>2–21<br>2–21<br>2–21<br>2–21<br>2–22 |

|   | 2.6                                                                | Combination of SMP16 and SMP Components                                                                                                                                                                                                                | 2–23                                                         |

|   | 2.7                                                                | List of References                                                                                                                                                                                                                                     | 2–26                                                         |

| 3 | AMS Sy                                                             | stem                                                                                                                                                                                                                                                   | 3–1                                                          |

|   | 3.1                                                                | System Overview                                                                                                                                                                                                                                        | 3–2                                                          |

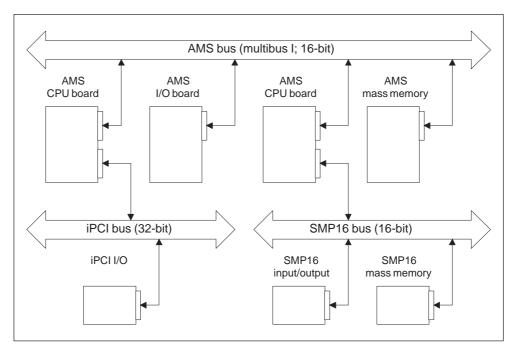

|   | 3.2<br>3.2.1<br>3.2.2                                              | Function Description         Bus Elements         Integration of the SMP16 and iPCI System in the AMS System                                                                                                                                           | 3–4<br>3–4<br>3–6                                            |

|   | 3.3                                                                | General Technical Description                                                                                                                                                                                                                          | 3–7                                                          |

|   | 3.4<br>3.4.1<br>3.4.2                                              | Signals of the Bus Interfaces<br>Information on Table LEERER MERKER<br>BDescription of the us Signals                                                                                                                                                  | 3–9<br>3–10<br>3–11                                          |

|   | 3.5<br>3.5.1<br>3.5.2<br>3.5.3<br>3.5.4                            | How the AMS Bus Functions<br>Initialization<br>Data Transmission<br>Interrupt Operation<br>Bus Allocation Control                                                                                                                                      | 3–16<br>3–16<br>3–16<br>3–18<br>3–19                         |

|   | 3.6                                                                | Combination of AMS, SMP16 and SMP Components                                                                                                                                                                                                           | 3–20                                                         |

| 4 | PCI Sys                                                   | tem                                                                                                                                                                                                         | 4–1                                                  |

|---|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

|   | 4.1<br>4.1.1<br>4.1.2<br>4.1.3                            | System Overview<br>Backplane Bus System<br>Located Expansion Bus<br>Nomenclature                                                                                                                            | 4–2<br>4–2<br>4–3<br>4–3                             |

|   | 4.2<br>4.2.1<br>4.2.2<br>4.2.3                            | iPCI System<br>General Technical Description<br>Implementation on SICOMP IMC<br>Signals of the Bus Interfaces                                                                                               | 4–4<br>4–4<br>4–8<br>4–10                            |

|   | 4.3<br>4.3.1<br>4.3.2                                     | Local PCI Expansion Bus<br>General<br>Signals of the PMC Module Interface                                                                                                                                   | 4–14<br>4–14<br>4–15                                 |

|   | 4.4                                                       | List of References                                                                                                                                                                                          | 4–16                                                 |

| 5 | Compac                                                    | t Computer                                                                                                                                                                                                  | 5–1                                                  |

| 6 | Assemb                                                    | ling Center                                                                                                                                                                                                 | 6–1                                                  |

| 7 | Power S                                                   | Supplies                                                                                                                                                                                                    | 7–1                                                  |

|   | 7.1                                                       | Connecting Plug Connector                                                                                                                                                                                   | 7–2                                                  |

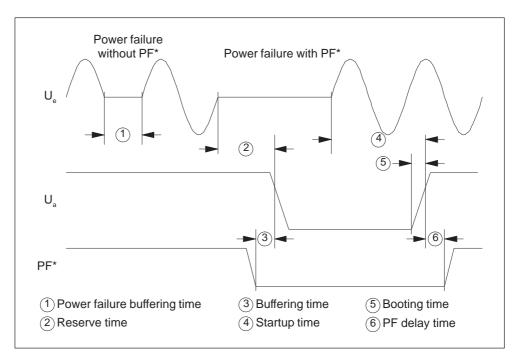

|   | 7.2<br>7.2.1<br>7.2.2<br>7.2.3                            | Electrical Characteristics<br>Electrical Operational Characteristics<br>Indications and Operation<br>Definition of Terms                                                                                    | 7–3<br>7–3<br>7–4<br>7–5                             |

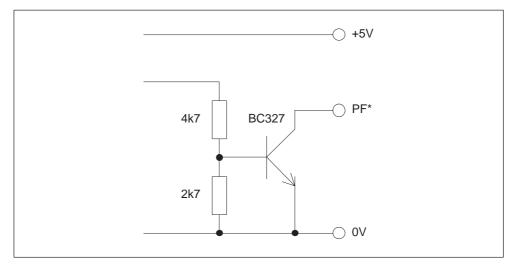

|   | 7.3                                                       | Power Failure Signaling                                                                                                                                                                                     | 7–8                                                  |

|   | 7.4<br>7.4.1<br>7.4.2                                     | Compatibility<br>Replacement Boards<br>Connection Compatibility                                                                                                                                             | 7–10<br>7–10<br>7–12                                 |

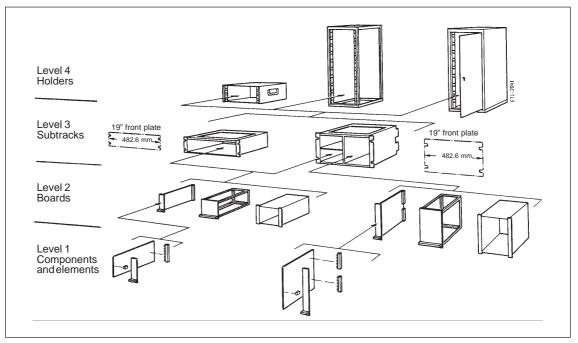

| 8 | System                                                    | Layout                                                                                                                                                                                                      | 8–1                                                  |

|   | 8.1                                                       | The Inch Layout System                                                                                                                                                                                      | 8–2                                                  |

|   | 8.2                                                       | Receptacles                                                                                                                                                                                                 | 8–3                                                  |

|   | 8.3<br>8.3.1<br>8.3.2<br>8.3.3<br>8.3.4<br>8.3.5          | Subracks<br>System Modules<br>Bus Backplanes<br>Bus Coupling Boards<br>Backup Battery<br>Mechanical Accessories                                                                                             | 8–4<br>8–6<br>8–8<br>8–9<br>8–10                     |

|   | 8.4                                                       | Boards                                                                                                                                                                                                      | 8–11                                                 |

|   | 8.5                                                       | Plug-In Connectors                                                                                                                                                                                          | 8–12                                                 |

|   | 8.6                                                       | Placement of the Boards in the System                                                                                                                                                                       | 8–23                                                 |

|   | 8.7<br>8.7.1<br>8.7.2<br>8.7.3<br>8.7.4<br>8.7.5<br>8.7.6 | Information on Mounting<br>Connecting the Guides<br>Mounting the Wiring Shield Plate<br>Bus Backplanes<br>Installing the Boards<br>Installing and Removing the Boards<br>Mounting the Cabinets and Housings | 8–25<br>8–25<br>8–26<br>8–26<br>8–27<br>8–28<br>8–29 |

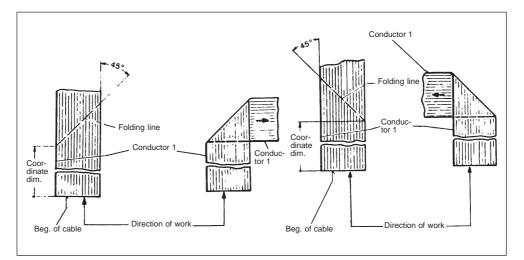

|    | 8.7.7                                                                                                   | Multiple-Row Systems, Special Systems and Cable Fabrication                                                                                                                                                                                                              | 8–29                                                                                         |

|----|---------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

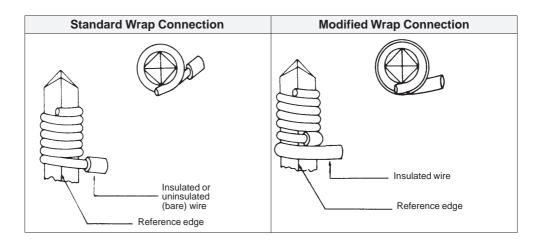

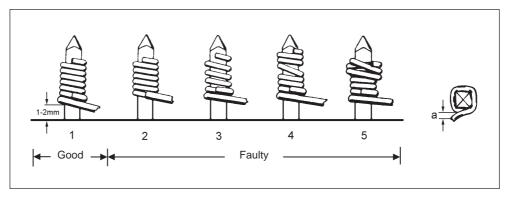

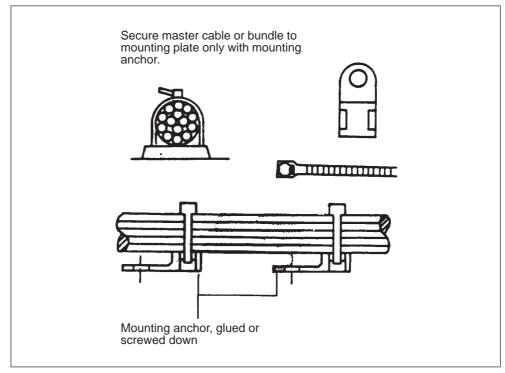

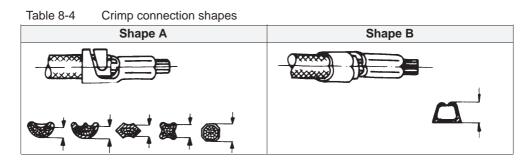

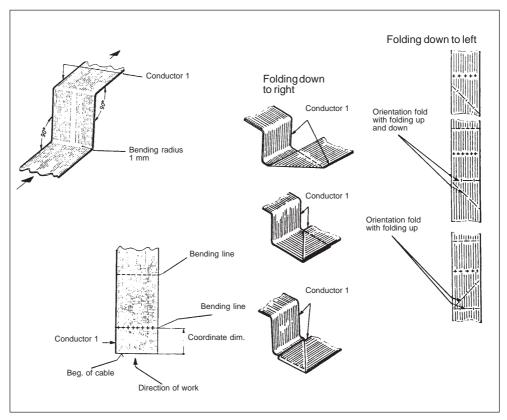

|    | 8.8<br>8.8.1<br>8.8.2<br>8.8.3<br>8.8.4<br>8.8.5<br>8.8.6<br>8.8.7<br>8.8.8<br>8.8.9<br>8.8.9<br>8.8.10 | Wiring<br>Baring of Cables<br>Tagging the Cable Ends<br>Wrap Connections<br>Wiring Cable Harnesses<br>Crimping<br>Insulation-Displacement-Connector Technique<br>Screw Connections<br>Plug-In Connections<br>Wiring the Power Supply on the Subrack<br>Line Installation | 8-30<br>8-30<br>8-30<br>8-33<br>8-33<br>8-36<br>8-40<br>8-41<br>8-41<br>8-43<br>8-43<br>8-47 |

| 9  | Softwar                                                                                                 | e                                                                                                                                                                                                                                                                        | 9–1                                                                                          |

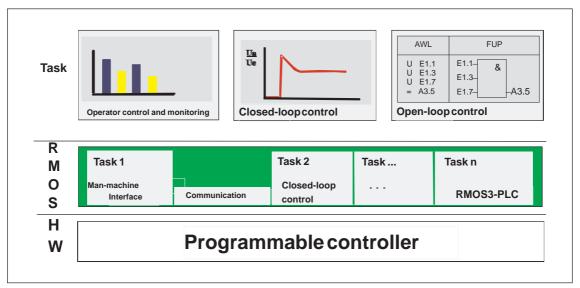

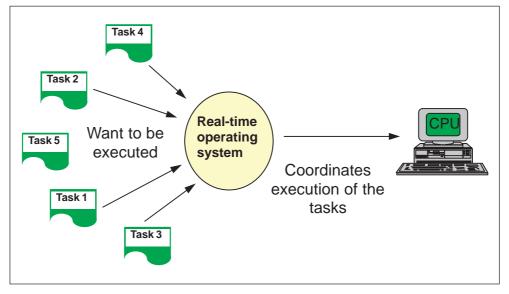

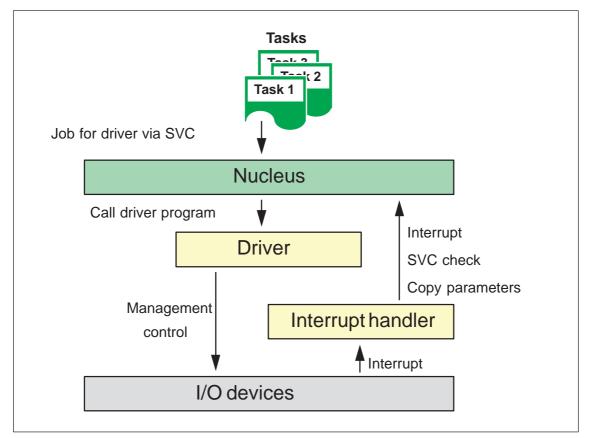

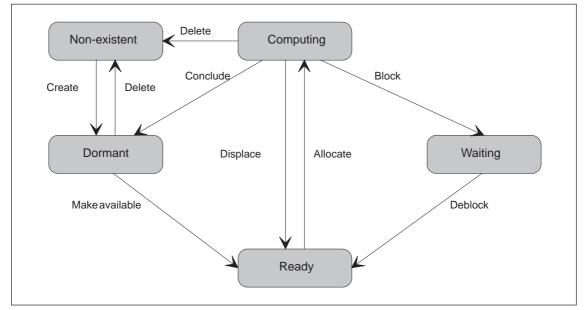

|    | 9.1<br>9.1.1<br>9.1.2<br>9.1.3<br>9.1.4<br>9.1.5                                                        | General Demands on Operating Systems Operating System Classes Automation Tasks Principles of Multitasking Task Communication and Coordination                                                                                                                            | 9–2<br>9–2<br>9–3<br>9–4<br>9–5<br>9–7                                                       |

|    | 9.2<br>9.2.1<br>9.2.2                                                                                   | Operating Systems Which Can Be Used<br>RMOS3<br>Other Operating Systems                                                                                                                                                                                                  | 9–9<br>9–9<br>9–9                                                                            |

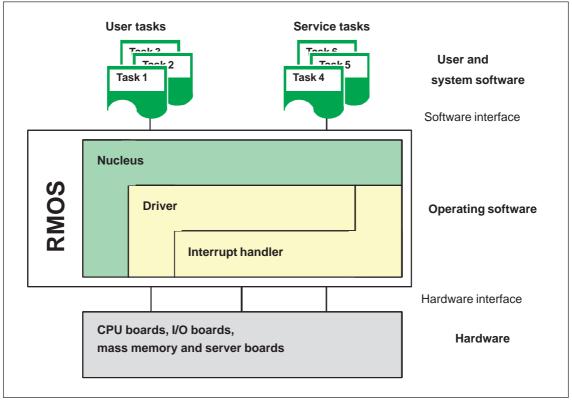

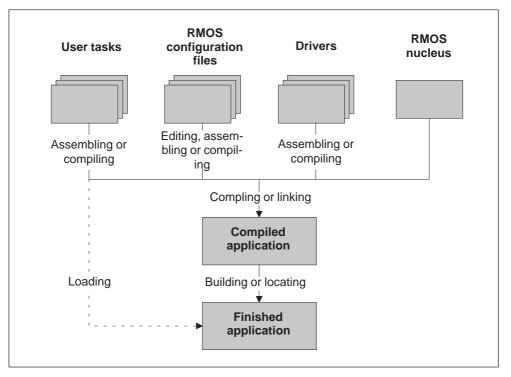

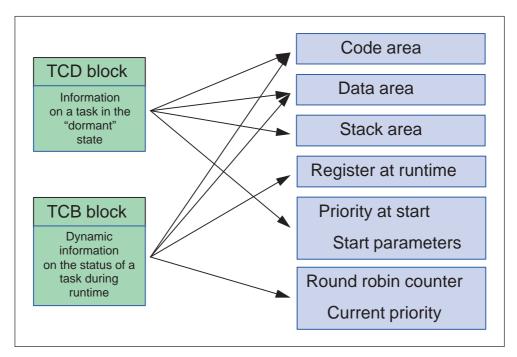

|    | 9.3<br>9.3.1<br>9.3.2<br>9.3.3<br>9.3.4<br>9.3.5                                                        | RMOS Operating System         Features of RMOS3         Components of RMOS         Management of Tasks         Configuration         Development Tools                                                                                                                   | 9–10<br>9–10<br>9–11<br>9–14<br>9–16<br>9–18                                                 |

|    | 9.4<br>9.4.1<br>9.4.2<br>9.4.3<br>9.4.4                                                                 | Standard Software<br>SMP16-AKO<br>Board Support Packages (BSPs)<br>RMOS3-PLC<br>Other                                                                                                                                                                                    | 9–19<br>9–19<br>9–20<br>9–20<br>9–20                                                         |

| 10 | Commu                                                                                                   | nication                                                                                                                                                                                                                                                                 | 10–1                                                                                         |

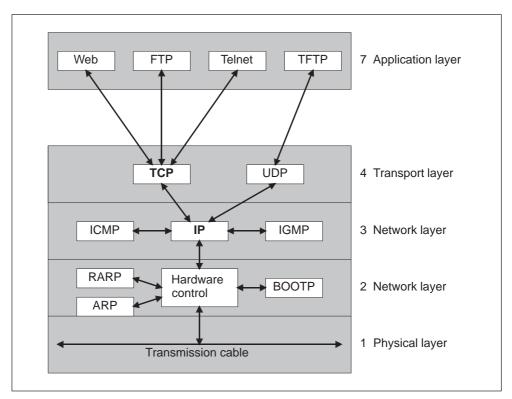

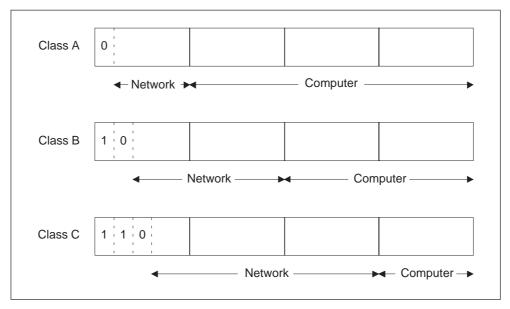

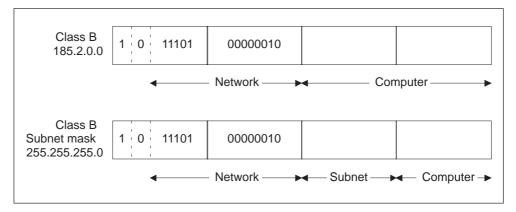

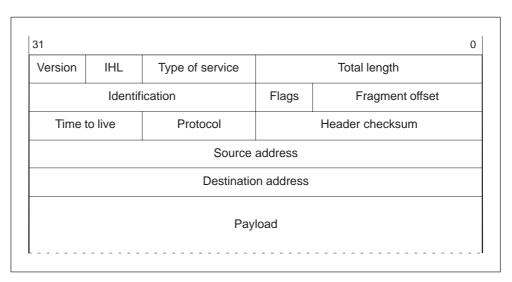

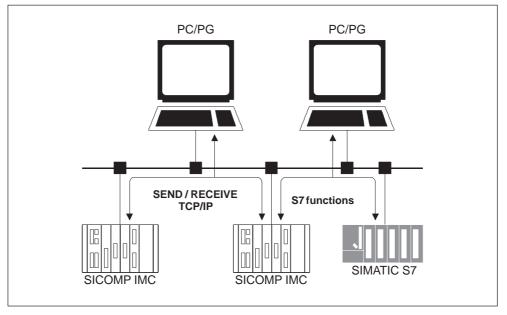

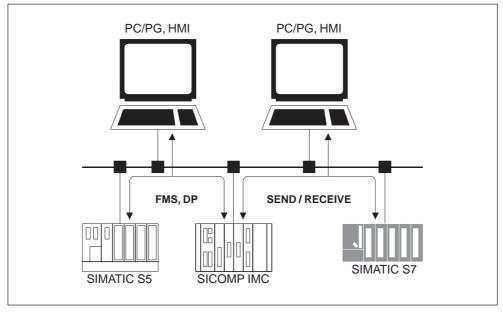

|    | 10.1<br>10.1.1<br>10.1.2<br>10.1.3                                                                      | Introduction and System Design<br>ISO Layer Model<br>TCP/IP Protocol<br>HTTP Protocol                                                                                                                                                                                    | 10–2<br>10–6<br>10–8<br>10–13                                                                |

|    | 10.2<br>10.2.1<br>10.2.2                                                                                | Industrial Ethernet<br>Layout<br>Industrial Ethernet Network Configurations                                                                                                                                                                                              | 10–14<br>10–15<br>10–16                                                                      |

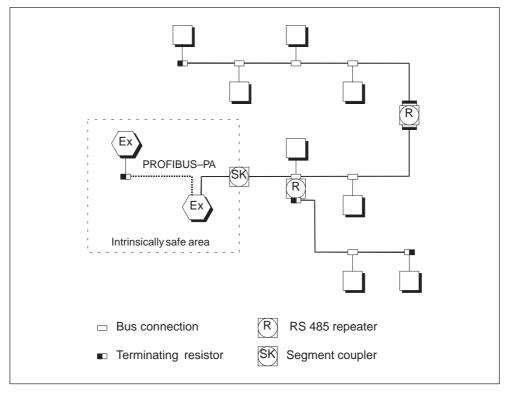

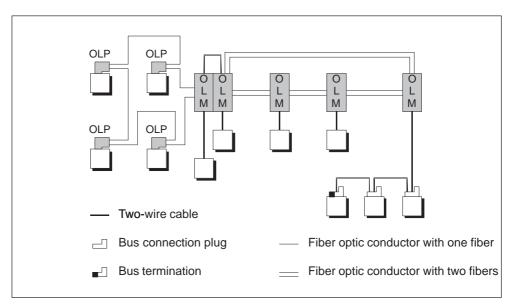

|    | 10.3<br>10.3.1<br>10.3.2                                                                                | PROFIBUS<br>Layout<br>PROFIBUS Network Configurations                                                                                                                                                                                                                    | 10–17<br>10–20<br>10–22                                                                      |

|    | 10.4<br>10.4.1<br>10.4.2<br>10.4.3                                                                      | Controller Area Network (CAN)<br>Physical Structure<br>Features of the Protocol<br>Summary                                                                                                                                                                               | 10–24<br>10–24<br>10–25<br>10–26                                                             |

|    | 10.5                                                                                                    | Remote Maintenance and Remote Diagnosis Via Internet                                                                                                                                                                                                                     | 10–27                                                                                        |

| 11 | Commis                                                                     | sioning, Testing and Debugging                                                                                                                                                                                                                                    | 11–1                                                 |

|----|----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

|    | 11.1                                                                       | Commissioning                                                                                                                                                                                                                                                     | 11–2                                                 |

|    | 11.2                                                                       | Commissioning the Hardware                                                                                                                                                                                                                                        | 11–2                                                 |

|    | 11.3<br>11.3.1<br>11.3.2<br>11.3.3                                         | Installing the Operating System                                                                                                                                                                                                                                   | 11–4<br>11–4<br>11–6<br>11–6                         |

|    | 11.4<br>11.4.1<br>11.4.2<br>11.4.3                                         | Parameterizing the Boards<br>Software Settings<br>Hardware Settings<br>Testing the Set Boards                                                                                                                                                                     | 11–6<br>11–7<br>11–8<br>11–8                         |

|    | 11.5<br>11.5.1<br>11.5.2                                                   | Commissioning an Application<br>Generating New Applications<br>System Expansions                                                                                                                                                                                  | 11–9<br>11–9<br>11–9                                 |

|    | 11.6                                                                       | Test and Debugging under RMOS                                                                                                                                                                                                                                     | 11–10                                                |

| 12 | Environ                                                                    | mental Requirements                                                                                                                                                                                                                                               | 12–1                                                 |

|    | 12.1                                                                       | General Information                                                                                                                                                                                                                                               | 12–2                                                 |

|    | 12.2                                                                       | Electrical Requirements                                                                                                                                                                                                                                           | 12–3                                                 |

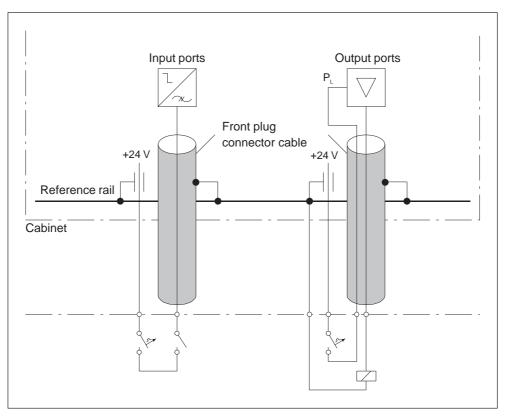

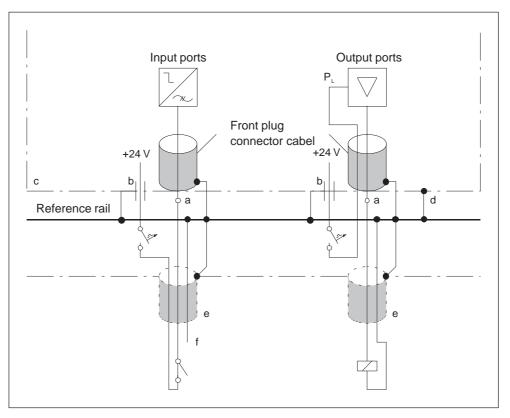

|    | 12.3<br>12.3.1<br>12.3.2<br>12.3.3                                         | Electro-Magnetic Compatibility<br>Requirements<br>Possible Sources of Interference<br>Measures for Suppression of Interference                                                                                                                                    | 12–4<br>12–4<br>12–5<br>12–5                         |

|    | 12.4                                                                       | Climatic Requirements                                                                                                                                                                                                                                             | 12–15                                                |

|    | 12.5                                                                       | Physical Requirements                                                                                                                                                                                                                                             | 12–16                                                |

|    | 12.6<br>12.6.1<br>12.6.2                                                   | Electrical Safety<br>Requirements at the System Level<br>Notes on System Integration                                                                                                                                                                              | 12–17                                                |

|    | 12.7                                                                       | EG Statement of Conformity                                                                                                                                                                                                                                        | 12–20                                                |

| 13 | Service/                                                                   | System Consulting/Training                                                                                                                                                                                                                                        | 13–1                                                 |

|    | 13.1                                                                       | Service                                                                                                                                                                                                                                                           | 13–2                                                 |

|    | 13.2<br>13.2.1<br>13.2.2<br>13.2.3<br>13.2.4<br>13.2.5<br>13.2.6<br>13.2.7 | Replacement Parts and Repairs .<br>Replacement Parts and Repair Service .<br>Delivery Dates for Replacement Parts Service .<br>Delivery Dates for Repair Service ("Naemlichkeit" Repairs) .<br>Delivery Releases .<br>Handling .<br>Warranty Times .<br>Packing . | 13–4<br>13–5<br>13–6<br>13–6<br>13–7<br>13–9<br>13–9 |

|    | 13.3                                                                       | Export Regulations                                                                                                                                                                                                                                                | 13–10                                                |

|    | 13.4                                                                       | Training Service                                                                                                                                                                                                                                                  | 13–11                                                |

| 14 | Glossar                                                                    | y/Abbreviations                                                                                                                                                                                                                                                   | G–1                                                  |

| 15 | Notes .                                                                    |                                                                                                                                                                                                                                                                   | 1                                                    |

# 1

# **SICOMP IMC System**

## Foreword

The open, PC-compatible SICOMP IMC system has been developed for industrial applications (e.g., measuring, and open and closed-loop control). Due to its sturdiness and universality, it is also being used increasingly for many other tasks. Tasks for which microcomputers are used are continuously increasing in scope and complexity. The demands placed on such a system are listed below.

- · Deterministic behavior and short reaction times

- Precise and fast acquisition and evaluation of measuring data

- High working speed

- Extensive controller functions

- · Interfaces to positioning systems and drives

- Unlimited communication capability (e.g., point-to-point, fieldbus or LAN/WAN)

- High degree of reliability and sturdiness

- · Easy to use

- Open to PC operating systems (e.g., Windows NT, Windows CE, and so on)

SICOMP IMC offers a wide variety of products and is the optimal basis for the applications and requirements listed below.

- Real-time applications using standard boards

- · Visualization of processes

- Very high computation capability

- · Highest demands on transparency of the logical structures

- Easy to expand

The hardware components of the SICOMP IMC include powerful, future-oriented and inexpensive compact devices – board systems SMP16 in single Europa format and AMS in double Europa format for 19-inch layout technology.

The bus systems have been optimally adapted to the requirements.

- SMP16 (8/16-bit) is an open, interference-immune and sturdy bus for I/O with a defined bus performance of up to 10 Mbyte/sec.

- AMS (16-bit) is a multi-master bus in accordance with Multibus I specifications.

- iPCI (32/64-bit) is an embedded standard PCI bus for highest data speeds up to 132 Mbyte/sec.

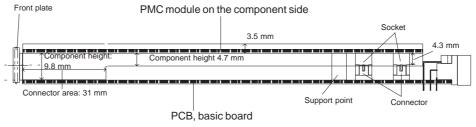

- PMC is a local bus for standardized PCI Mezzanine Cards.

The board systems have been coordinated to permit the advantages of the compact SMP16 boards and multiprocessor-capable AMS boards to be combined in one frame. With the AMS, the transparent local bus concept based on SMP16 or iPCI permits integration of two or more bus systems in one frame. PMC modules can be integrated in both the SMP16 and AMS systems.

SICOMP IMC is also flexible when it comes to operating systems. It can handle Windows NT, Windows CE, the RMOS real-time operating system, and any other operating systems based on the PC platform. SICOMP IMC ensures an unusual amount of freedom – from full PC compatibility to optimized embedded solutions.

# 2

# SMP16 System

#### **Table of Contents**

| 2.1                                                                | System Overview                                                                                                                                                                                                                                        | 2-2                                                          |

|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| 2.2<br>2.2.1<br>2.2.2                                              | Function Description<br>Bus Elements<br>System Architecture                                                                                                                                                                                            | 2-5<br>2-5<br>2-6                                            |

| 2.3                                                                | General Technical Description                                                                                                                                                                                                                          | 2-8                                                          |

| 2.4<br>2.4.1<br>2.4.2                                              | Signals of the Bus Interface<br>Explanation of Table 2-4<br>Description of the Bus Signals                                                                                                                                                             | 2-9<br>2-10<br>2-11                                          |

| 2.5<br>2.5.1<br>2.5.2<br>2.5.3<br>2.5.4<br>2.5.5<br>2.5.6<br>2.5.7 | Data Transmission on the Bus<br>General Description<br>Data Bus Length<br>Control of the Data Bus Length with IOCS16* and MEMCS16*<br>Read Operations<br>Write Operations<br>Slave-Master Synchronization with RDYIN<br>Command Delays and Wait Cycles | 2-19<br>2-19<br>2-20<br>2-21<br>2-21<br>2-21<br>2-21<br>2-22 |

| 2.6                                                                | Combination of SMP16 and SMP Components                                                                                                                                                                                                                | 2-23                                                         |

| 2.7                                                                | List of References                                                                                                                                                                                                                                     | 2-26                                                         |

# 2.1 System Overview

## The SICOMP SMP16 system

The SICOMP SMP16 system is a further development of the modular SMP board system which has proven itself in long years of industrial use. Like the original system, this system offers reliability, continuity and constant innovative further development.

The SICOMP SMP16 bus is compatible with the over 150 SICOMP SMP boards on the market today.

Use of the SICOMP SMP16 boards permits flexible automation systems to be set up quickly. This provides extra time to write the application software.

The SMP16 bus is a synchronous mono master bus with 16-bit data bus, 20-bit address bus and various signal lines. These control the memory and input/output accesses. The memory area which can be addressed by the SMP16 bus can contain up to 1 Mbytes. In addition, for applications which make extensive use of inputs/outputs, there are 64 Kbytes for direct inputs/outputs and 4 Kbytes for memory input/output (MMIO).

Depending on the board used, a choice of 8-bit or 16-bit data transfers is available. The SMP16 bus supports one and two-cycle DMA transfers for high-speed data transmission. This permits specific data transfers with minimum system load at the time of the transfer.

Another feature of the SMP16 bus is its flexible support of interrupts. Its open structure permits interrupts to be handled as simple point-to-point connections or cascaded in master/slave operation.

# Products

The following types of products are available with SICOMP SMP16.

- Boards

- Operating system software

- Board support packages

- Additional parts and accessories

Boards are delivered with or without firmware depending on the application area.

Board support packages contain board-specific software (firmware) in the form of EPROM blocks and/or installation and driver software on floppy disk. In addition, documentation on commissioning is included.

#### Advantages of the SMP16 bus system

- Further development of the familiar and reliable SMP bus (industrial standard)

- Its simple functions provide powerful bus interfaces with low bus interface costs.

- The timing of the SMP16 bus increases bus performance without compromising compatibility with existing components.

- Physically, the SMP16 offers the advantages of the well-known concept of the single Europa card format and indirect connection. The layout of very powerful systems is compact, and an optimized price/performance ratio is maintained at the same time.

- Since bus pins which can be wired as desired permit flexible use of special functions (e.g., large interrupt systems), the SMP16 bus is very suited to industrial real-time applications with very short reaction times.

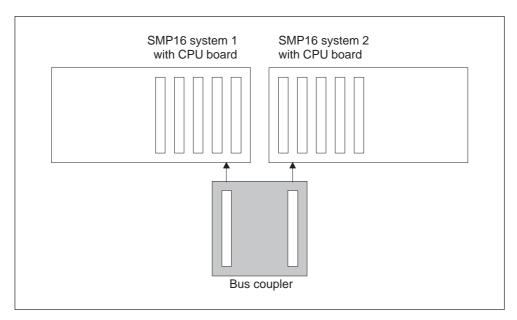

- Using coupling modules, two separate SMP16 systems can be connected. In addition, a bus coupler can be used to increase the number of slots for slave boards.

- The SMP16 bus offers efficient methods of process visualization and utilization

of a wide variety of software based on MS-DOS or RMOS. It can be used as a

stand-alone unit (I/O expansion) and together with a second SMP16 CPU (via a

coupler module). In addition, it can be used as a universal hardware platform

on which various operating systems can be run. The components of the

SMP16 bus are available individually and as a ready-to-use industrial system

from the Assembling Center.

### Innovations of the SMP16 system in comparison to the SMP system

- Data bus was expanded to 16 bits. In comparison to the SICOMP SMP, bus performance has been increased by a factor of 3 to 5 with the SICOMP SMP16.

- Prepared for the new generation of integrated circuits which require a 3.3 V voltage supply

- Bus timing was revised and made uniform.

- Any PC-compatible SMP16 CPU can handle any SMP16 board. PC-compatible I/O functions on the SMP16 bus must adhere to the SMP16 timing specifications. These boards (graphics and LAN) can also be operated on non-PC systems. Some of the slower I/O boards can be handled by the CPU via wait cycles and command delays which can be set.

- Gross bus transfer speed was increased to up to 10 Mbyte/sec.

- Special signal allocation was made uniform.

- PC timing was integrated so that powerful real-time PCs can be generated on an SMP16 basis.

- The SMP16 bus is compatible with the SMP bus (i.e., with few exceptions, existing SMP components can continue to be used with the SMP16 bus. See chapter 2.6.

- EMC compatibility was increased. All SMP16 boards have CE certification.

- Metal front facings are equipped with single locking.

- Guaranteed adherence to bus timing for modern SMP16 I/O boards with the ASIC (ASBIC) bus interface

- Using the ASBIC, wrap wiring on the I/O boards was largely replaced by software settings. For automatic configuration, see chapter 11.

- High computer performance due to latest CPU boards

# 2.2 Function Description

# 2.2.1 Bus Elements

#### Primary bus master (CPUs)

Master boards (CPUs also) are boards which are able to actively initiate or execute a data transfer to or from the slave boards. The user activates the control signals of the system and provides a valid address.

Primary bus masters usually always have control over the bus. However, bus control can be temporarily turned over to a secondary bus master for DMA cycles. While the secondary bus master has control of the bus, the primary bus master remains passive on the bus.

The SMP16 bus only permits one primary bus master (i.e., mono-master bus).

#### Secondary bus master

Secondary bus masters are controllers which are not located with the primary master on one board but whose functions sometimes require control of the SMP16 bus (e.g., DMA controller boards).

The user requests bus control from the primary bus master. The secondary bus master cannot begin data transfer operations until the primary bus master releases the bus.

If several secondary bus masters exist, they themselves must provide for arbitration of conflicting accesses. The SMP16 bus does not provide arbitration. If this mode is desired, make sure that the primary bus master also supports this mode.

#### SMP16 slave boards

SMP16 slave boards evaluate the address signals supplied by the master and react to its control signals.

SMP16 slave boards cannot be bus masters.

#### PC-compatible SMP16 slave boards

PC-compatible SMP16 slave boards support special PC-compatible input/output bus cycles marked by an inactive BUSEN signal and the status of the AEN signal.

These boards permit conventional PC I/O functions such as PC-compatible networks, graphics (e.g., VGA) and so on. These boards can also be configured so that they can be used with non PC-compatible bus masters.

When PC-compatible SMP16 slave boards are also to be used with standard SMP16 bus masters, they must meet valid SMP16 specifications [1].

# 2.2.2 System Architecture

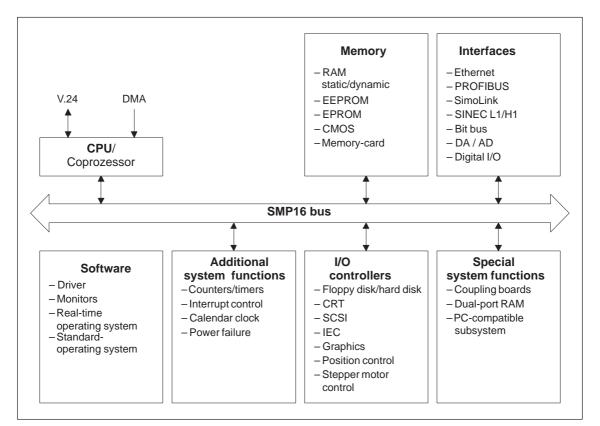

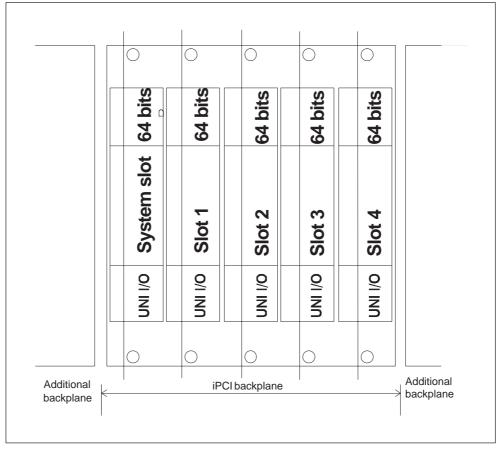

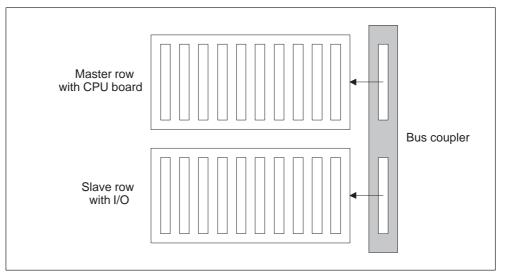

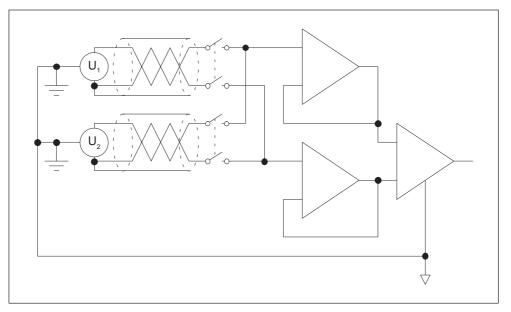

Figure 2-1 System architecture of the SICOMP SMP/SMP16 bus

| SMP16 System Data                      |                                                                                                                                                      |  |  |  |

|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| System configuration                   | Mono-master system with DMA capability                                                                                                               |  |  |  |

| System bus                             | Synchronous bus, separate address/data lines                                                                                                         |  |  |  |

| Transfer speed                         | ≤ 10 Mbyte/sec                                                                                                                                       |  |  |  |

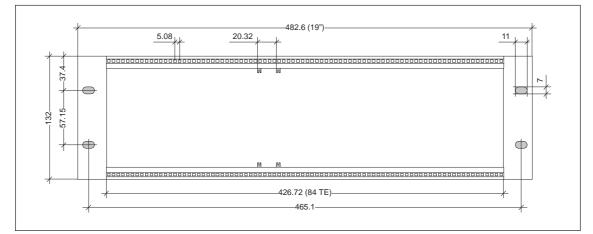

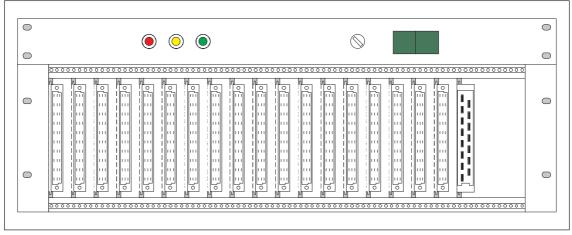

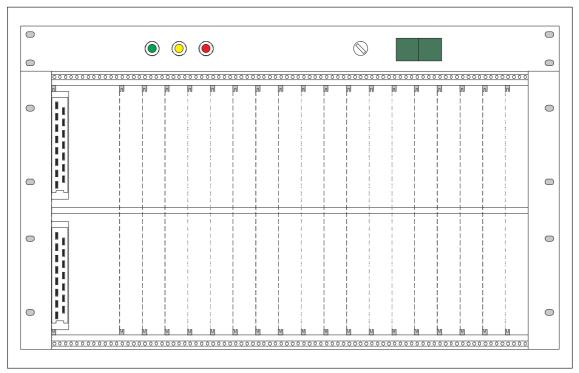

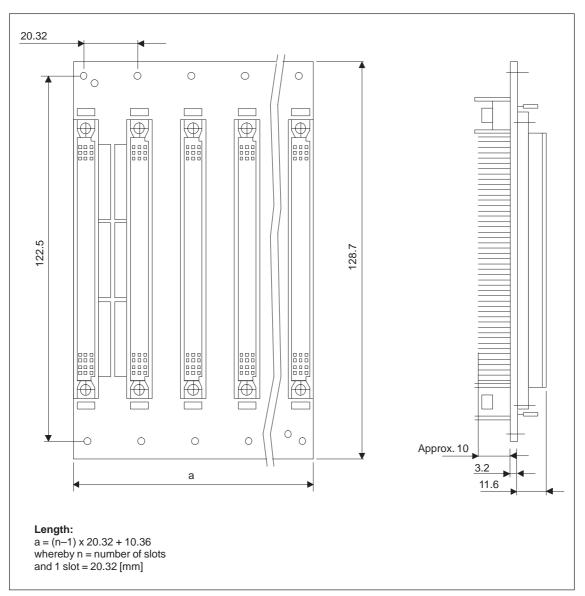

| Slots                                  | Max. of 21 per 19-inch system subrack                                                                                                                |  |  |  |

| Data size                              | 8 or 16 bits                                                                                                                                         |  |  |  |

| Address areas                          | <ol> <li>1-Mbyte memory address area</li> <li>64-Kbyte input/output address area</li> <li>4-Kbyte memory input/output address area (MMIO)</li> </ol> |  |  |  |

| Interrupt system                       | Depends on CPU used                                                                                                                                  |  |  |  |

| Multiple computer configuration        | Dual-port RAM coupling in a system frame with sepa-<br>rate backplanes                                                                               |  |  |  |

| Methods of bus coupling                | SMP16 – SMP16. See chapter 8.                                                                                                                        |  |  |  |

| Board configuration                    | Via ASBIC per software, via local registers or wrap settings                                                                                         |  |  |  |

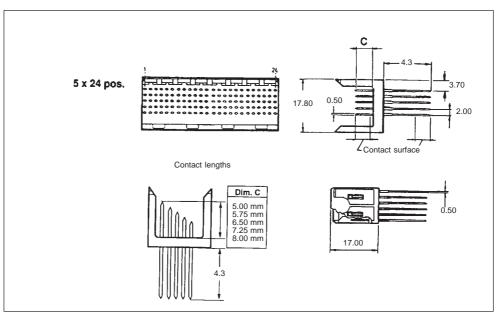

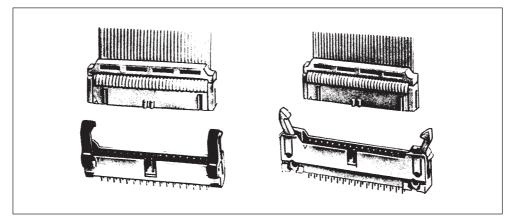

| Plug connection system                 | Indirect, 96-pin, in acc. w. DIN 41612                                                                                                               |  |  |  |

| EMC and environment compati-<br>bility | CE conformance. See chapter 12.                                                                                                                      |  |  |  |

| Fan                                    | No fan. Exception: High-performance CPUs). See chapter 12.4.                                                                                         |  |  |  |

| Backup battery                         | See chapter 8.                                                                                                                                       |  |  |  |

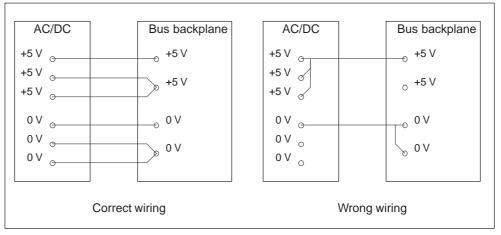

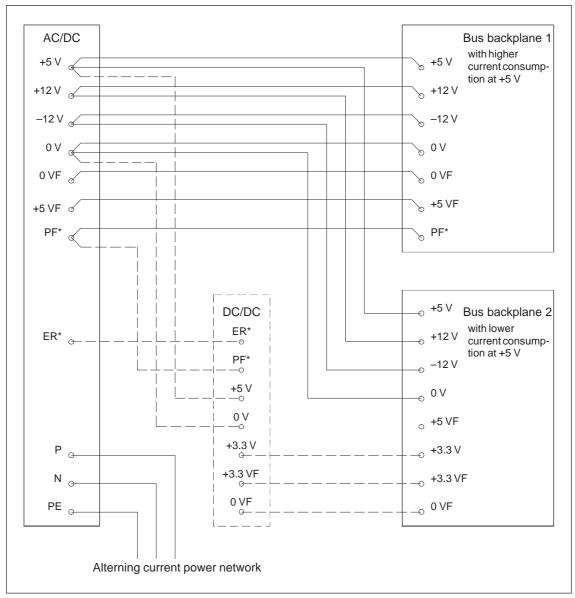

| Supply voltages                        | +5 V, ±5 %<br>+3.3 V, ±5 % (optional) <sup>1)</sup><br>±12 V, ±5 % (optional)<br>±15 V, ±3 % (optional)                                              |  |  |  |

Table 2-1 SMP16 system data

1) Specific boards may have different requirements.

#### Table 2-2 Nomenclature

| Nomenclature            |           |  |  |  |

|-------------------------|-----------|--|--|--|

| Communication boards    | SMP16-COM |  |  |  |

| CPU boards              | SMP16-CPU |  |  |  |

| I/O controller          | SMP16-CTR |  |  |  |

| Input/output boards     | SMP16-EA  |  |  |  |

| Input/output modules    | SMP16-EAM |  |  |  |

| Memory boards           | SMP16-MEM |  |  |  |

| Special function boards | SMP16-SFT |  |  |  |

| Power supplies          | SMP16-SV  |  |  |  |

| Mechanics components    | SMP16-SYS |  |  |  |

| Rack boards for modules | SMP16-TBG |  |  |  |

| Accessories             | SMP16-ZUB |  |  |  |

# 2.3 General Technical Description

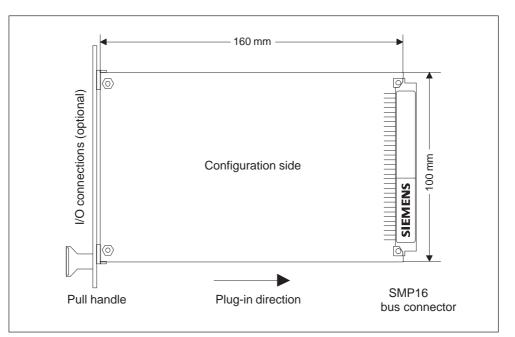

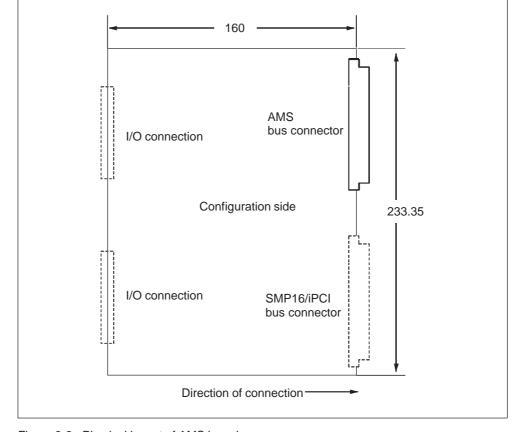

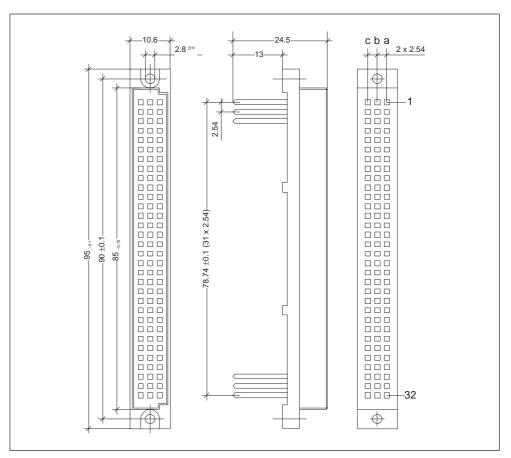

Figure 2-2 Physical layout of SMP16 boards

| Dime                                               | Dimensions of SMP16 Boards                                                                                                       |  |  |  |  |

|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Length                                             | 160 mm                                                                                                                           |  |  |  |  |

| Height                                             | 100 mm                                                                                                                           |  |  |  |  |

| Thickness of the PCB                               | 1.6 mm (±0.2 mm)                                                                                                                 |  |  |  |  |

| Front plate                                        | Aluminium, 2.5 mm thick                                                                                                          |  |  |  |  |

| Max. height of the components                      | 14 mm                                                                                                                            |  |  |  |  |

| Length of the connections or                       | Max. of 2.0 mm                                                                                                                   |  |  |  |  |

| thickness of the components on the back of the PCB | At least 2.5 mm free on the upper and lower edge of<br>the PCBs so that the boards can be pushed freely<br>along the guide rails |  |  |  |  |

| Locking                                            | Single locking with screws                                                                                                       |  |  |  |  |

| Pull handle                                        | Fixed pull handle with space for labeling (e.g., logo or board designation)                                                      |  |  |  |  |

| I/O plug connector                                 | Connectors suitable for the functions, usually sub D technology                                                                  |  |  |  |  |

| Color of the outside                               | Ergo gray                                                                                                                        |  |  |  |  |

| Mounting dimensions                                | In acc. w. internal specifications                                                                                               |  |  |  |  |

| Labeling                                           | In acc. w. internal specifications                                                                                               |  |  |  |  |

| Accessories                                        | Short front plate for installation in systems with total locking                                                                 |  |  |  |  |

| Front system                                       | Flat front plate with fixed pull handle                                                                                          |  |  |  |  |

|                                                    |                                                                                                                                  |  |  |  |  |

| Table 2-3 | Dimensions ( | of SMP16 boards    |

|-----------|--------------|--------------------|

| 10010 2-0 |              | JI SIVIL TO DUALUS |

# 2.4 Signals of the Bus Interface

| Pin | Pin                 | Pin Row A |        |                        | Pin Row B |                   |       | Pin Row C |       |  |

|-----|---------------------|-----------|--------|------------------------|-----------|-------------------|-------|-----------|-------|--|

|     | Signal              | Circ      | uiting | Signal Circuiting      |           | Signal Circuiting |       |           |       |  |

| 1   | –15 V               | V2        | -      | A16                    | V1        | R1                | –12 V | V2        | -     |  |

| 2   | +3.3 V              | V3        | -      | A17                    | V1        | R1                | GND   | V3        | -     |  |

| 3   | -                   | -         | -      | AEN                    | -         | -                 | +5 V  | V3        | -     |  |

| 4   | CLK                 | V1        | R1     | _                      | -         | -                 | MMIO* | V1        | R1    |  |

| 5   | MEMCS16*            | V1        | R1     | DREQ0*                 | _         | -                 | A12   | V1        | R1    |  |

| 6   | RESET*              | V1        | R1     | DREQ1*                 | -         | -                 | A0    | V1        | R1    |  |

| 7   | ALE                 | V1        | R1     | DACK0*                 | -         | -                 | A13   | V1        | R1    |  |

| 8   | MEMR*               | V1        | R1/Z1  | DACK1* 1)              | -         | -                 | A1    | V1        | R1    |  |

| 9   | RESIN*              | V1        | -      | _                      | -         | -                 | A14   | V1        | R1    |  |

| 10  | MEMW*               | V1        | R1/Z1  | _                      | _         | -                 | A2    | V1        | R1    |  |

| 11  | _                   | _         | _      | Reserved <sup>2)</sup> | _         | -                 | A15   | V1        | R1    |  |

| 12  | RDYIN               | V1        | R1     | PWFAIL*                | -         | -                 | A3    | V1        | R1    |  |

| 13  | BUSEN               | V1        | R1     | Reserved <sup>2)</sup> | -         | R1                | NMI*  | -         | -     |  |

| 14  | DB0                 | V1        | R1     | +3.3 V                 | V3        | -                 | A4    | V1        | R1    |  |

| 15  | HOLDA <sup>3)</sup> | V1        | R1     | +5 V                   | V3        | -                 | IRQ0* | -         | -     |  |

| 16  | DB1                 | V1        | R1     | GND                    | V3        | -                 | A5    | V1        | R1    |  |

| 17  | HOLD* 3)            | V1        | R1     | GND                    | V3        | -                 | IRQ1* | -         |       |  |

| 18  | DB2                 | V1        | R1     | _ 3)                   | _         | -                 | A6    | V1        | R1    |  |

| 19  | INT*                | V1        | R1     | ICAS0 3) 4)            | -         | -                 | IRQ2* | -         | -     |  |

| 20  | DB3                 | V1        | R1     | ICAS1 3) 4)            | -         | -                 | A7    | V1        | R1    |  |

| 21  | IOCS16*             | V1        | R1     | ICAS2 3) 4)            | _         | -                 | IRQ3* | -         | -     |  |

| 22  | DB4                 | V1        | R1     | DB8                    | V1        | R1                | A8    | V1        | R1    |  |

| 23  | INTA*               | V1        | R1     | DB9                    | V1        | R1                | IRQ4* | -         | -     |  |

| 24  | DB5                 | V1        | R1     | DB10                   | V1        | R1                | A9    | V1        | R1    |  |

| 25  | UBAT                | V1        | -      | DB11                   | V1        | R1                | IRQ5* | -         | -     |  |

| 26  | DB6                 | V1        | R1     | DB12                   | V1        | R1                | A10   | V1        | R1    |  |

| 27  | 0WS                 | V1        | _      | DB13                   | V1        | R1                | IRQ6* | -         | -     |  |

| 28  | DB7                 | V1        | R1     | DB14                   | V1        | R1                | A11   | V1        | R1    |  |

| 29  | TC/EOP*             | V1        | -      | DB15                   | V1        | R1                | IRQ7* | -         | -     |  |

| 30  | IOW*                | V1        | R1/Z1  | BHEN                   | V1        | R1                | IOR*  | V1        | R1/Z1 |  |

| 31  | +15 V               | V2        | _      | A18                    | V1        | R1                | GND   | V3        | -     |  |

| 32  | +5 V                | V3        | _      | A19                    | V1        | R1                | +12 V | V2        | _     |  |

Table 2-4 Signal assignment for the SMP16 bus

1) Is supplied by some CPUs as special signal OSC

2) Reserved for special signals ACEN (b11) and ACDONE (b13). See chapter 2.6.

3) Bus lines can also be used for DACK\* and DREQ\* signals or for DMA cascading.

4) Can be used to cascade interrupts (alternate to footnote 3)

# 2.4.1 Explanation of Table 2-4

# "Signal" columns

If names are specified here, the connections are allocated with these bus signals. An asterisk (\*) after the name indicates a low-active signal.

A dash (–) means that boards can allocate special signals to the connection.

Reserved connections are provided for future or special applications and may not be allocated with special signals.

# "Circuiting" columns

The left-hand columns show the links established by the bus backplane. The righthand columns show the connection circuiting on the bus backplane.

| Connection  | Meaning                                                                                                                         |

|-------------|---------------------------------------------------------------------------------------------------------------------------------|

| V1          | Narrow cable on the bus backplane which connects connections with the same connection row and number for all bus slots          |

| V2          | Wide cable on the bus backplane which connects connections with the same connection row and number for all bus slots            |

| V3          | Connection with a through conductor level on the bus backplane                                                                  |

| -           | Non-through connection                                                                                                          |

| Termination | Meaning                                                                                                                         |

| R1          | Termination of the cable on the bus backplane located at this connection with a pull-up resistor of 3.3 k $\Omega$ against +5 V |

| Z1          | Termination of the cable on the bus backplane located at this connection with an RC element                                     |

| -           | No circuiting                                                                                                                   |

# 2.4.2 Description of the Bus Signals

The following tables use the abbreviations and symbols shown below.

| Signal Direction | Meaning                                                               |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------|--|--|--|--|--|

| Z > P            | From CPU <sup>1)</sup> to I/O                                         |  |  |  |  |  |

| P > Z            | From I/O to CPU                                                       |  |  |  |  |  |

| Z <> P           | Bi-directional signal flow between CPU and I/O                        |  |  |  |  |  |

| P <> P           | Bi-directional signal flow between I/O boards                         |  |  |  |  |  |

| Characteristic   | Requirements on Outputs for This Signal                               |  |  |  |  |  |

| OC               | Open collector                                                        |  |  |  |  |  |

|                  | OC outputs can assume two signal states:<br>LOW or high ohmic         |  |  |  |  |  |

| TP               | Totem pole                                                            |  |  |  |  |  |

|                  | TP outputs can assume two signal states:<br>LOW or HIGH               |  |  |  |  |  |

| TS               | Tri state                                                             |  |  |  |  |  |

|                  | TS outputs can assume three signal states:<br>LOW, HIGH or high ohmic |  |  |  |  |  |

Table 2-5 Explanation of the abbreviations and symbols

1) Primary or secondary bus master

#### Control signals of the SMP16 bus

Control signals are all signals required for correct handling of data communication. Control signals permit activation of memory blocks, data transmission to and from input/output blocks (direct addressing or MMIO), and the control of I/O devices (e.g., acknowledgment signals for interrupts and DMA).

| Signal | Signal<br>Direction | Characteri-<br>stic | Function                                                                                                                                         |

|--------|---------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| ALE    | Z > P               | TP                  | "Address latch enable"                                                                                                                           |

|        |                     |                     | The ALE signal was used on slave boards for latching of address lines A0 to A19. It is usually activated at the beginning of an SMP16 bus cycle. |

|        |                     |                     | Since some bus masters do not or do not always support it, it may no longer be used by new slave boards.                                         |

|        |                     |                     | Due to compatibility, the signal line of the ALE must remain reserved.                                                                           |

Table 2-6 Control signals of the SMP16 bus

| Table 2-6 | Control signals of the SMP16 bus, continued |                     |                                                                                                                                                                                                                              |  |

|-----------|---------------------------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Signal    | Signal<br>Direction                         | Characteri-<br>stic | Function                                                                                                                                                                                                                     |  |

| BHEN      | Z > P                                       | TS/TP               | "Byte high enable"                                                                                                                                                                                                           |  |

|           |                                             |                     | Control signals to enable information communication on the more significant part of the data bus (DB8 to DB15)                                                                                                               |  |

|           |                                             |                     | The BHEN signal indicates a real 16-bit access to an even address (A0 =0) of the memory or the input/output area. This signal is always inactive for 8-bit accesses.                                                         |  |

| BUSEN     | Z > P                                       | TP                  | "Bus enable"                                                                                                                                                                                                                 |  |

|           |                                             |                     | Control signal to distinguish between CPU and special accesses                                                                                                                                                               |  |

|           |                                             |                     | The inactive BUSEN signal prevents slave boards from de-<br>coding the address lines directly in the input/output area. In<br>this case, these boards can be selected via special signals<br>(e.g., DACK* for DMA transfer). |  |

|           |                                             |                     | The BUSEN signal can be disregarded for memory or MMIO* accesses.                                                                                                                                                            |  |

| CLK       | Z > P                                       | TP                  | "Clock"                                                                                                                                                                                                                      |  |

|           |                                             |                     | System clock pulse on the CPU                                                                                                                                                                                                |  |

|           |                                             |                     | This signal is generated by the primary bus master and may not exceed 12 MHz.                                                                                                                                                |  |

| HOLDA     | Z > P                                       | TP                  | "Hold acknowledge"                                                                                                                                                                                                           |  |

| HOLD*     | P > Z                                       | ТР                  | "Hold"                                                                                                                                                                                                                       |  |

|           |                                             |                     | These signals are used to transfer the SMP16 bus from the primary bus master to a secondary bus master (i.e., to a DMA controller on a slave board).                                                                         |  |

|           |                                             |                     | The secondary bus master requests bus rights by activating<br>the HOLD* signal. If the primary bus master supports this<br>function, it transfers rights to the secondary bus master by<br>activating the HOLDA signal.      |  |

|           |                                             |                     | For DMA function, see also DREQ*/DACK* in table LEERER MERKER.                                                                                                                                                               |  |

| IOCS16*   | P > Z                                       | OC                  | "Input/output chip select 16"                                                                                                                                                                                                |  |

|           |                                             |                     | This signal tells the bus master whether the slave board ad-<br>dressed via address lines A0 to A15 in the input/output ad-<br>dress area is able to perform a 16-bit access.                                                |  |

| IOR*      | Z > P                                       | TS/TP               | "I/O read"                                                                                                                                                                                                                   |  |

|           |                                             |                     | Control signal of the CPU to read information using the direct input/output procedure. The input/output address area contains 64 Kbytes.                                                                                     |  |

| IOW*      | Z > P                                       | TS/TP               | "I/O write"                                                                                                                                                                                                                  |  |

|           |                                             |                     | Control signal of the CPU to write information using the direct input/output procedure. The input/output address area contains 64 Kbytes.                                                                                    |  |

Table 2-6

Control signals of the SMP16 bus, continued

| Signal   | Signal<br>Direction | Characteri-<br>stic | Function                                                                                                                                                                                                                                                                                                                                                                            |

|----------|---------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MEMCS16* | P > Z               | OC                  | "Memory chip select 16"                                                                                                                                                                                                                                                                                                                                                             |

|          |                     |                     | This signal tells the bus master whether the slave board ad-<br>dressed via address lines A0 to A19 (or via A0 to A11 together<br>with MMIO*) in the memory address area is able to perform a<br>16-bit access.                                                                                                                                                                     |

|          |                     |                     | Bus masters which support the IOCS16* and MEMCS16* signals automatically divide the 16-bit access (triggered by the SW) into two byte accesses when the addressed slave board does not activate any of the signals (appropriate to the type of access) as soon as it recognizes its address. IOCS16* and MEMCS16* may only be activated by slave boards at even addresses (A0 = 0). |

|          |                     |                     | The IOCS16* and MEMCS16* signals are required for a 16-bit transfer between SMP16 slave boards and PC-compatible SMP16 bus masters.                                                                                                                                                                                                                                                 |

| MEMR*    | Z > P               | TS/TP               | "Memory read"                                                                                                                                                                                                                                                                                                                                                                       |

|          |                     |                     | Control signal of the CPU to read information from a 1-Mbyte memory address area of the SMP16 bus                                                                                                                                                                                                                                                                                   |

|          |                     |                     | If the MMIO* signal is active at the same time, input/output boards which use the so-called memory input/output proce-<br>dure are addressed.                                                                                                                                                                                                                                       |

| MEMW*    | Z > P               | TS/TP               | "Memory write"                                                                                                                                                                                                                                                                                                                                                                      |

|          |                     |                     | Control signal of the CPU to write information to a 1-Mbyte memory address area of the SMP16 bus                                                                                                                                                                                                                                                                                    |

|          |                     |                     | If the MMIO* signal is active at the same time, input/output boards which use the so-called memory input/output proce-<br>dure are addressed.                                                                                                                                                                                                                                       |

| MMIO*    | Z > P               | TP                  | "Memory Mapped I/O"                                                                                                                                                                                                                                                                                                                                                                 |

|          |                     |                     | This signal can be used to address slave boards via an ad-<br>dress window in the 1-Mbyte memory address area of the<br>SMP16 bus.                                                                                                                                                                                                                                                  |

|          |                     |                     | When direct input/output accesses are used, its status can be active (LOW) or inactive (HIGH).                                                                                                                                                                                                                                                                                      |